什么是缓存总线(Cache Bus)?

高速缓存总线是计算机处理器用来与其高速缓存通信的专用高速总线。也称为后端总线,其运行速度比系统总线快得多。高速缓存总线直接将处理器内核连接到其高速缓存;它独立于处理器总线运行,在更宽的范围内传输数据,路径限制...

高速缓存总线是计算机处理器用来与其高速缓存通信的专用高速总线。也称为后端总线,其运行速度比系统总线快得多。高速缓存总线直接将处理器内核连接到其高速缓存;它独立于处理器总线运行,在更宽的范围内传输数据,路径限制较少。大多数现代处理器使用缓存总线来减少读取或修改频繁访问的数据所需的时间。

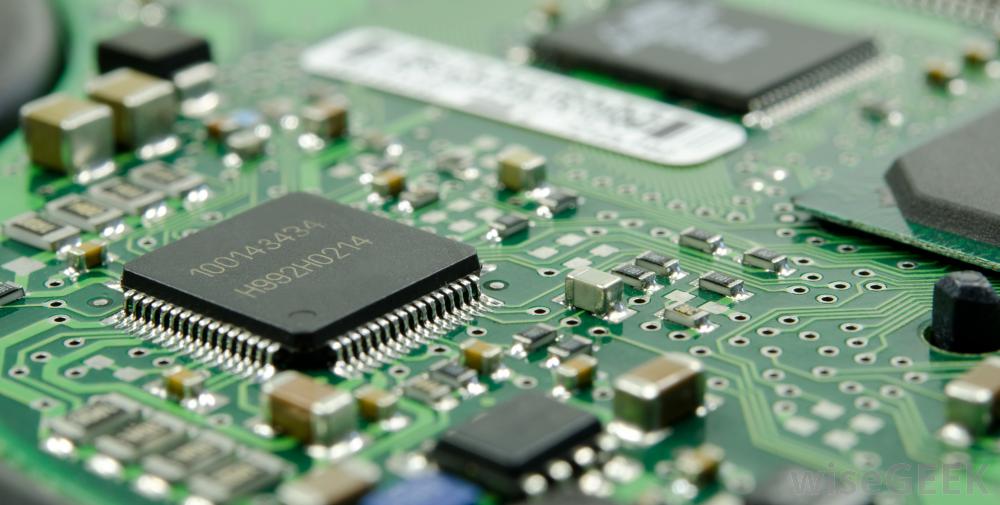

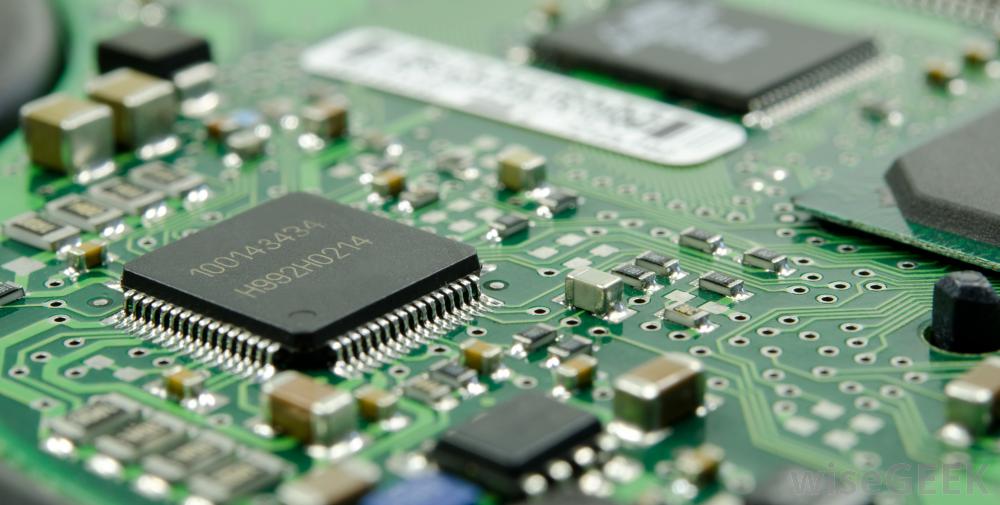

计算机处理器使用缓存总线与其高速缓存进行通信。

计算机处理器使用缓存总线与其高速缓存进行通信。

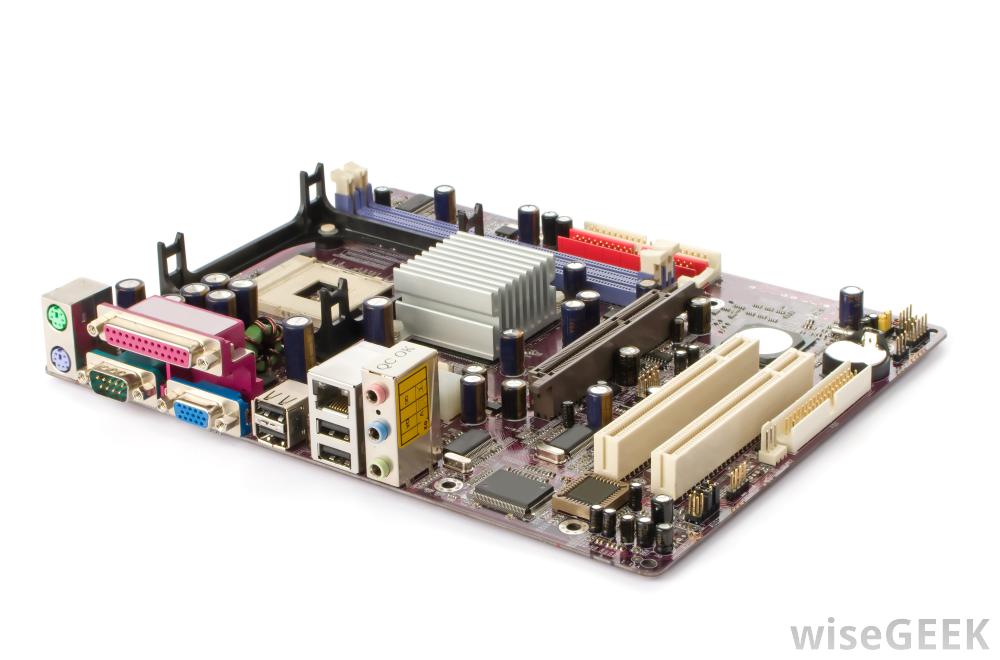

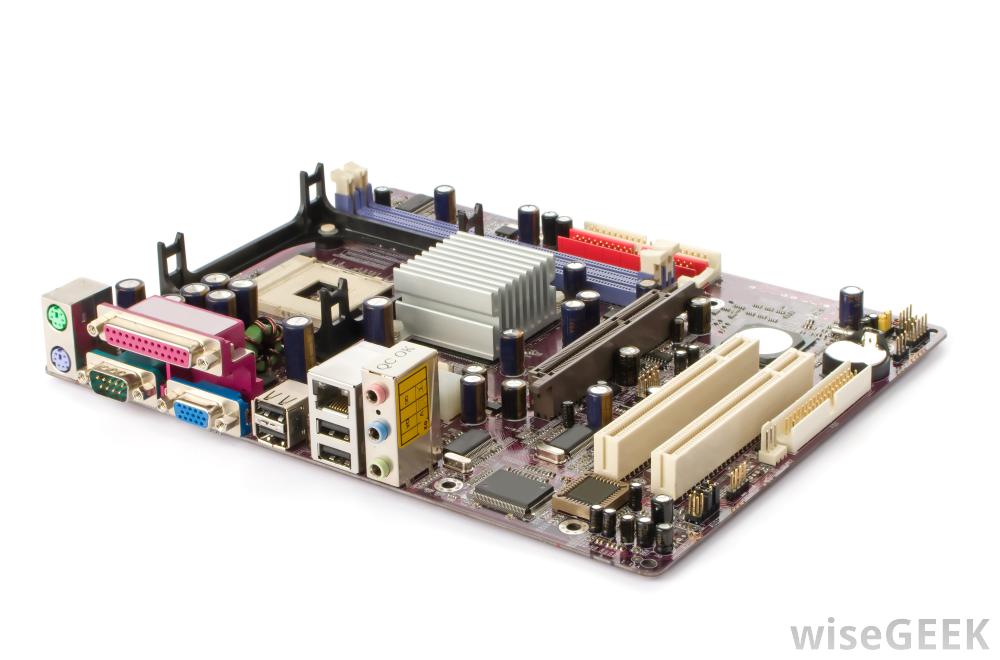

,缓存通常位于主板上,而不是处理器芯片上。缓存是通过处理器总线访问的,与常规系统内存一样,缓存内存的数量通常非常小,仅作为可选的系统性能增强提供。

,缓存通常位于主板上,但现在缓存更常见地内置在CPU芯片中。

,缓存通常位于主板上,但现在缓存更常见地内置在CPU芯片中。

随着上世纪90年代初处理器速度和效率的提高,处理器总线成为一个瓶颈;快速缓存需要一种与处理器交互的方式,而无需等待更慢的系统内存上世纪90年代中期,大多数新处理器采用了双总线结构来解决这个问题。一个高速缓存总线被用来直接访问缓存。这个总线不用于其他任何事情所有其他数据传输都使用较慢的处理器总线,也被称为前端总线。处理器可以同时使用两条总线,从而获得更好的性能

早期的双总线设计经常使用位于主板上的高速缓存;由于产量问题,大量的片上缓存还不具备成本效益。后来的设计通常会将内部和外部缓存结合起来,以提高产量。现代处理器通常会使用大量的内部缓存;与通常只有8千字节(KB)的旧设计相比,许多缓存包括8兆字节(MB)或更多。在现代设计中,整个缓存都在芯片上,缓存总线可以非常短,数据路径非常宽,在某些处理器中为512位。总线通常以与处理器本身相同的速度运行。其最终结果是可以非常快地读取或修改缓存内容。

多核处理器的每个内核可能有自己的缓存或共享一个大的公共缓存。在这两种情况下,缓存总线将每个内核连接到相应的缓存内存。当每个处理器内核都有自己独立的缓存时,可能会出现一致性问题。例如,当一个内核更新其缓存中的数据时,其他缓存中该数据的其他副本将过期或"过时"。解决此类问题的一种方法是使用一种特殊类型的缓存总线,有时称为核心间总线。该总线将所有缓存链接在一起,以便在更新共享数据时,每个缓存都可以监视其他缓存正在执行的操作,其他的可以立即反映新内容。

计算机处理器使用缓存总线与其高速缓存进行通信。

计算机处理器使用缓存总线与其高速缓存进行通信。,缓存通常位于主板上,而不是处理器芯片上。缓存是通过处理器总线访问的,与常规系统内存一样,缓存内存的数量通常非常小,仅作为可选的系统性能增强提供。

,缓存通常位于主板上,但现在缓存更常见地内置在CPU芯片中。

,缓存通常位于主板上,但现在缓存更常见地内置在CPU芯片中。随着上世纪90年代初处理器速度和效率的提高,处理器总线成为一个瓶颈;快速缓存需要一种与处理器交互的方式,而无需等待更慢的系统内存上世纪90年代中期,大多数新处理器采用了双总线结构来解决这个问题。一个高速缓存总线被用来直接访问缓存。这个总线不用于其他任何事情所有其他数据传输都使用较慢的处理器总线,也被称为前端总线。处理器可以同时使用两条总线,从而获得更好的性能

早期的双总线设计经常使用位于主板上的高速缓存;由于产量问题,大量的片上缓存还不具备成本效益。后来的设计通常会将内部和外部缓存结合起来,以提高产量。现代处理器通常会使用大量的内部缓存;与通常只有8千字节(KB)的旧设计相比,许多缓存包括8兆字节(MB)或更多。在现代设计中,整个缓存都在芯片上,缓存总线可以非常短,数据路径非常宽,在某些处理器中为512位。总线通常以与处理器本身相同的速度运行。其最终结果是可以非常快地读取或修改缓存内容。

多核处理器的每个内核可能有自己的缓存或共享一个大的公共缓存。在这两种情况下,缓存总线将每个内核连接到相应的缓存内存。当每个处理器内核都有自己独立的缓存时,可能会出现一致性问题。例如,当一个内核更新其缓存中的数据时,其他缓存中该数据的其他副本将过期或"过时"。解决此类问题的一种方法是使用一种特殊类型的缓存总线,有时称为核心间总线。该总线将所有缓存链接在一起,以便在更新共享数据时,每个缓存都可以监视其他缓存正在执行的操作,其他的可以立即反映新内容。

- 发表于 2020-07-10 16:04

- 阅读 ( 1651 )

- 分类:电脑网络

你可能感兴趣的文章

- 什么是多功能打印机(Multifunction Printer)? 1667 浏览

- 什么是数据挖掘(Data Mining)? 1077 浏览

- 什么是访问控制矩阵(Access Control Matrix)? 3078 浏览

- 什么是复写本(Carbon Copy)? 1985 浏览

- 计算机犯罪有哪些不同类型(Different Types of Computer Crime)? 1111 浏览

- 什么是IP模块(IP Module)? 2305 浏览

- 什么是影子公羊(Shadow RAM)? 1049 浏览

- 什么是USB路由器适配器(USB Router Adapter)? 1270 浏览

- 什么是超频(Overclocking)? 1476 浏览

- 什么是内容联合(Content Syndication)? 1447 浏览

- 什么是内部调制解调器(Internal Modem)? 1178 浏览

- 什么是视频艺术(Video Art)? 1363 浏览

- 对计算机的安全威胁有什么不同(Different Threats to Computer Security)? 852 浏览

- 在HTML中,什么是标记(In HTML, what is Tagging)? 983 浏览

- 虚拟机有哪些不同类型(Different Types of Virtual Machines)? 1472 浏览

- 以太网适配器有哪些不同类型(Different Types of Ethernet Adapters)? 944 浏览

- 如何选择最好的VBScript编辑器(Choose the Best VBScript Editor)? 1186 浏览

- 什么是替代键盘(Alternative Keyboard)? 1181 浏览

- 什么是多核处理(Multi-Core Processing)? 2411 浏览

- 什么是机器感知(Machine Perception)? 3025 浏览

- 什么是直接映射(Direct Mapping)? 2295 浏览

- 如何重新启动计算机(I Reboot a Computer)? 1535 浏览

- 我如何将两张图片变形在一起(Morph Two Pictures Together)? 1092 浏览

- 什么是密码猴(Code Monkey)? 1375 浏览

- 什么是隐私模式(Privacy Mode)? 2575 浏览

- 什么是卫星宽带(Satellite Broadband)? 1487 浏览

- AutoCAD的不同用途是什么(Different Uses of AutoCAD&Reg;)? 1119 浏览

- 什么是网络电话(Internet Phone)? 968 浏览

- 什么是银行转换(Bank Switching)? 1190 浏览

- 把硬盘放在冰箱里有好处吗(Is It Beneficial to Put a Hard Drive in the Freezer)? 1424 浏览

相关问题

0 条评论

请先 登录 后评论

admin

0 篇文章

作家榜 »

-

xiaonan123

189 文章

xiaonan123

189 文章

-

汤依妹儿

97 文章

汤依妹儿

97 文章

-

luogf229

46 文章

luogf229

46 文章

-

jy02406749

45 文章

jy02406749

45 文章

-

小凡

34 文章

小凡

34 文章

-

Daisy萌

32 文章

Daisy萌

32 文章

-

我的QQ3117863681

24 文章

我的QQ3117863681

24 文章

-

华志健

23 文章

华志健

23 文章

推荐文章

- 什么是交错(Interleaving)?

- 什么是神经网络(Neural Network)?

- 什么是4D鼠标(4D Mouse)?

- 什么是CAD建模(CAD Modeling)?

- 什么是WiFi网络(WiFi&Reg; Network)?

- 什么是电子数据处理(Electronic Data Processing)?

- 微处理器是如何工作的(Microprocessors Work)?

- 什么是家庭网络服务器(Home Network Server)?

- 火线端口会过时吗( FireWire&Reg; Ports Becoming Obsolete)?

- 什么是总线电缆(Bus Cable)?

- 什么是记忆棒(Memory Stick)?

- 如何选择最好的家庭网络设置(Choose the Best Home Network Setup)?

- 什么是存档位(Archive Bit)?

- 软件工程过程的步骤是什么(Steps in the Software Engineering Process)?

- 什么是自由软件基金会(Free Software Foundation)?

- 什么是数据隐藏(Data Hiding)?

- 什么是闪存卡(Flash Card)?

- 如何选择最佳的网络接口卡(Choose the Best Network Interface Card)?

- 如何防止CPU过热(Prevent CPU Overheating)?

- 什么是雪鞋垃圾邮件(Snowshoe Spamming)?

- 火线连接器有哪些不同类型(Different Types of FireWire® Connectors)?

- 什么是SRAM(SRAM)?

- 什么是并行操作系统(Parallel Operating Systems)?

- 什么是神经处理(Neural Processing)?

- 什么是Web数据库(Web Database)?

- 有哪些不同类型的大容量存储设备(Different Types of Mass Storage Devices)?

- 电信产品有哪些不同类型(Different Types of Telecommunications Products)?

- 什么是控制逻辑(Control Logic)?

- 什么是手工编码(Hand Coding)?

- 流媒体有哪些不同类型(Different Types of Streaming Media)?